GitHub Repository

GitHub Repository

Overview

This project involved designing and implementing a digital electronic combination lock system using VHDL (VHSIC Hardware Description Language). The system required entering a 4-digit code on a numeric keypad to unlock the mechanism. The project demonstrated comprehensive hardware description skills and advanced understanding of digital system design principles.

System Architecture

The electronic lock consists of several interconnected components:

- Input Interface: A 16-key numeric keypad connected to a 16-bit data bus.

- Encoder: Translates keypad input into 4-bit binary code.

- Character Detector: Detects key presses and activates the signal processing.

- Memory System: Four 4-bit registers that store consecutive key presses.

- Comparator: Verifies if the entered 4-digit code matches the predefined key (1234).

- Output Control: Generates an unlock signal when the correct code is entered.

Implementation Details

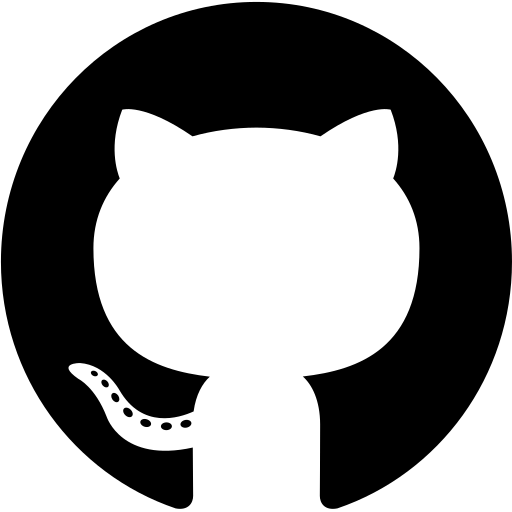

1. Encoder Component

- Implemented a 16-to-4 encoder that converts one-hot coded keypad inputs to 4-bit binary values

- Designed truth tables for all possible key press combinations

- Created VHDL behavioral model with conditional signal assignments

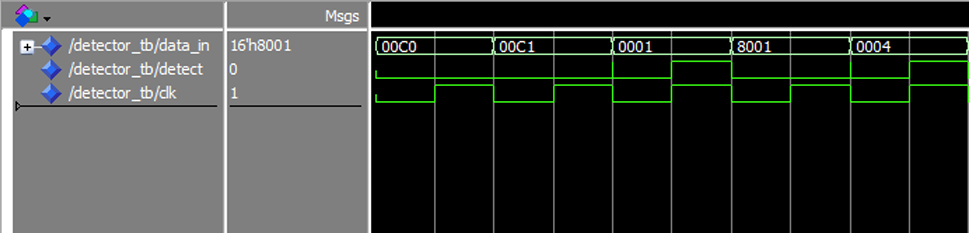

2. Character Detector

- Built a detector circuit that signals when any key is pressed

- Synchronized detection with system clock for reliable operation

- Implemented with combinational logic to ensure fast response times

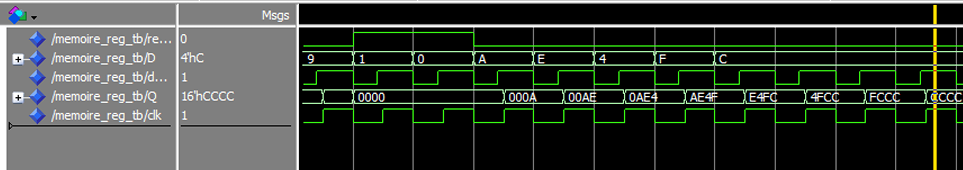

3. Memory Subsystem

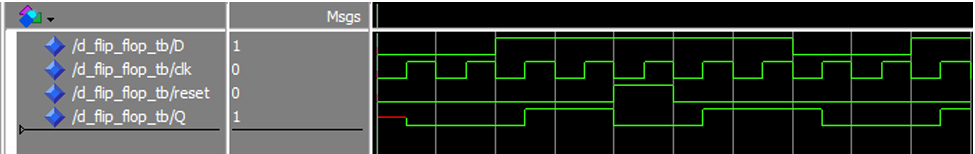

- Designed D flip-flops with asynchronous reset functionality

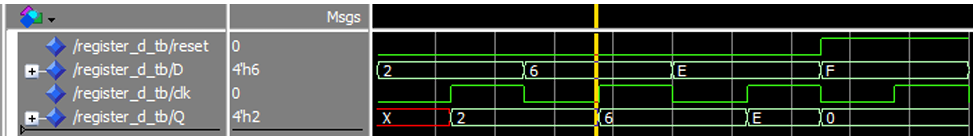

- Created 4-bit registers by combining four D flip-flops

- Implemented a shift register system to store successive key presses

- Developed memory management for a complete 16-bit (4-digit) code

4. Comparator Circuit

- Designed a 4-bit comparator for equality checking

- Extended the design to create a full 16-bit comparator

- Implemented hard-coded reference value (1234) for security verification

- Created logical operations to generate the unlock signal when codes match

5. System Integration

- Designed a structural architecture connecting all components

- Created signal pathways between components for data flow

- Implemented synchronous operation using a central clock

- Added reset capability for security and usability

Simulation and Testing

All components were thoroughly tested using ModelSim, with test benches developed for each module:

- Created comprehensive test vectors for the encoder and detector

- Verified D flip-flop behavior with clock and reset signals

- Tested register functionality with various input patterns

- Validated comparator accuracy with matching and non-matching codes

- Performed full system integration testing with complete code entry sequences

Technologies Used

- VHDL: Hardware description language for digital circuit design

- ModelSim: Simulation environment for testing and verification

- IEEE VHDL Libraries: Standard logic libraries for component development

- Combinational and Sequential Logic Design: Fundamental digital design methodologies

- Quartus (optional): For synthesis and implementation on FPGA platforms

Results and Outcomes

The electronic lock system was successfully implemented and demonstrated the following capabilities:

- Accurate detection and encoding of numeric keypad inputs

- Proper storage of successive key presses in the memory system

- Correct comparison of entered codes against the predefined key

- Reliable unlock signal generation for matching codes

- Robust operation under various input sequences

The final system successfully simulated a practical electronic combination lock with a 4-digit security code. The implementation demonstrated both sequential and combinational logic design in VHDL and showcased the integration of multiple digital components into a functional embedded system.

Contributors

- Errouji Oussama

- Imad-Eddine NACIRI